# On Hardware-based Security in Embedded Systems

## Evaluating potential use of secure hardware in C-ITS stations

## DIPLOMARBEIT

zur Erlangung des akademischen Grades

## **Diplom-Ingenieur**

im Rahmen des Studiums

#### **Technische Informatik**

eingereicht von

### Gerhard Hechenberger, BSc.

Matrikelnummer 01326157

an der Fakultät für Informatik

der Technischen Universität Wien

Betreuung: Privatdoz. Mag.rer.soc.oec. Dipl.-Ing. Dr.techn. Edgar Weippl Mitwirkung: Dipl.-Ing. Herbert Fuereder

Wien, 21. Jänner 2020

Gerhard Hechenberger

Edgar Weippl

# On Hardware-based Security in Embedded Systems

## Evaluating potential use of secure hardware in C-ITS stations

**DIPLOMA THESIS**

submitted in partial fulfillment of the requirements for the degree of

## **Diplom-Ingenieur**

in

#### **Computer Engineering**

by

Gerhard Hechenberger, BSc.

Registration Number 01326157

to the Faculty of Informatics

at the TU Wien

Advisor: Privatdoz. Mag.rer.soc.oec. Dipl.-Ing. Dr.techn. Edgar Weippl Assistance: Dipl.-Ing. Herbert Fuereder

Vienna, 21<sup>st</sup> January, 2020

Gerhard Hechenberger

Edgar Weippl

## Erklärung zur Verfassung der Arbeit

Gerhard Hechenberger, BSc.

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit – einschließlich Tabellen, Karten und Abbildungen –, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Wien, 21. Jänner 2020

Gerhard Hechenberger

## Danksagung

Ich möchte mich bei meinem Betreuer Prof. Weippl für die Möglichkeit bedanken, diese Arbeit umsetzen zu können, als auch für seine Anleitung während dieser Zeit. Bei meiner Chefin Karin und meinen Arbeitskollegen Herbert and Thomas möchte ich mich ebenfalls bedanken, für ihre Unterstützung in organisatorischen sowie technischen Belangen. In meiner Zeit als Werkstudent bei Siemens habe ich wirklich viel von ihnen gelernt. Ein spezielles Danke geht auch an meinen langjährigen Freund Luca, für seine andauernde Unterstützung in Zeiten stressiger Semester und anstrengenden Prüfungsvorbereitungen. Nicht zuletzt möchte ich meinen Eltern Martin und Brigitta danken, für ihre vorbehaltlose menschliche und finanzielle Unterstützung, die mir so viele Möglichkeiten eröffnet hat. Ohne sie wäre diese Arbeit nie möglich gewesen.

## Acknowledgements

I want to thank my adviser Prof. Weippl for the possibility of creating this work and his guidance, as also my boss Karin and my colleagues Herbert and Thomas for their support on organizational and technical means. I really learned a lot from them during my time as a working student at Siemens. A special thanks also goes to my long friend Luca for his enduring support during stressful semesters and tough exam preparations. Finally, I want to thank my parents Martin and Brigitta, for their unconditional support on social and financial matters which offered me so many opportunities. Without them, this work would have never been possible.

## Kurzfassung

Collaborative Intelligent Transport Systems (C-ITS) Stationen sind aktuell aufkommende Internet of Things (IoT) Geräte im Bereich der Verkehrsinformation und -kontrolle. Überwiegend befestigt an Straßenkreuzungen werden sie genutzt, um Vehicle-to-everything (V2X) Nachrichten zu senden und weiterzuleiten und über unterschiedlichste Kanäle zu kommunizieren. Durch den Stellenwert der Safety bei Verkehrsinfrastruktur ist hier Security sehr wichtig. Zusätzlich sind Geräte, die den Angreifern physikalischen Zugang ermöglichen, speziell exponiert und benötigen Security-Maßnahmen, die durch Hardware unterstützt werden.

In unserer Arbeit zur Verbesserung der Security in C-ITS Stationen der nächsten Generation analysieren wir zuerst basierend auf IEC 62443 System- und Service-Anforderungen und erstellen eine Threat and Risk Analysis (TRA). Danach untersuchen wir die Verfügbarkeit und Funktionalität von Security-Hardware-Modulen, um ein in ein ganzheitliches System-Security Konzept eingebettetes, Hardware-unterstütztes Key-Management zu entwickeln. Durch die Implementierung auf einem NXP i.MX8QXP Evaluation Kit erreichen wir Einblick in die Ausgereiftheit der Software, den Entwicklungsprozess sowie potenzielle Stolperfallen und Probleme der sicheren System-Entwicklung.

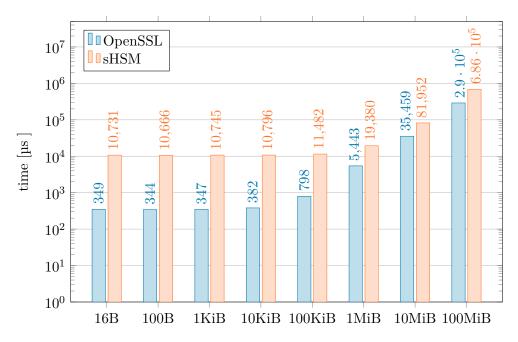

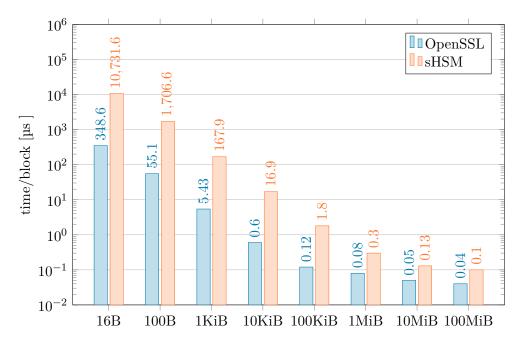

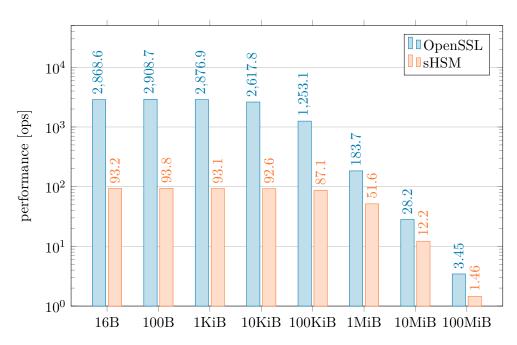

Unser entwickeltes Konzept erfüllt unsere Anforderungen und zeigt signifikante Verbesserungen in der TRA. Allerdings muss durch die Nutzung eines Trusted Execution Environments (TEEs), wie erwartet, bei der Verschlüsselungs-Performance im Vergleich zu OpenSSL ein Rückgang um Faktor 30 für kleine Datenmengen und 2.4 für große Datenmengen akzeptiert werden. Während unserer Untersuchung konnten wir mehrere Implementierungsmängel in der verfügbaren Software entdecken, die sowohl Funktionalität als auch Security betreffen. Für einige davon bieten wir Lösungsvorschläge an und beschäftigen uns schlussendlich noch mit den nötigen Schritten zur Übernahme in den Produktiv-Betrieb.

**Schlüsselwörter** — Collaborative Intelligent Transport Systems, RSU, Hardware security modules, Embedded systems security, Secure boot, Secure key management, U-Boot, OP-TEE, i.MX8

## Abstract

Collaborative Intelligent Transport Systems (C-ITS) stations are recently upcoming Internet of Things (IoT) devices in the domain of traffic information and control. Meant to be deployed at intersections, they are working as highly heterogeneous routing devices to send and relay Vehicle-to-everything (V2X) messages. As traffic infrastructure poses safety implications, security is particularly important here. Additionally, devices which give physical access to attackers are especially exposed and require security measures which need the underlying hardware's support.

In our work to improve security in the next generation of C-ITS stations, we first analyze for system and service requirements based on IEC 62443 and conduct a Threat and Risk Analysis (TRA). We then survey the market about available secure hardware modules and its provided functionalities, to be able to set up a hardware-supported secure key management embedded in a full system-security concept. Implementing this using an NXP i.MX8QXP evaluation kit lets us gain further insights about its software maturity, the development process and potential pitfalls and problems of secure systems engineering.

Our created concept satisfies the given requirements and shows to significantly improve the TRA. However, as expected due to the usage of a Trusted Execution Environment (TEE), encryption performance suffered from a drop of factor 30 for small files to a drop of about factor 2.4 for big files in a comparison against OpenSSL. During our research, we also discover multiple implementation shortcomings of the provided software concerning functionality and security, propose fixes and summarize the steps needed to move to production.

**Keywords** — Collaborative Intelligent Transport Systems, RSU, Hardware security modules, Embedded systems security, Secure boot, Secure key management, U-Boot, OP-TEE, i.MX8

# Contents

| Kurzfassung  |                            |                                  |      |  |  |  |

|--------------|----------------------------|----------------------------------|------|--|--|--|

| $\mathbf{A}$ | bstra                      | $\mathbf{ct}$                    | xiii |  |  |  |

| 1            | Intr                       | oduction                         | 1    |  |  |  |

|              | 1.1                        | Motivation and Problem Statement | 1    |  |  |  |

|              | 1.2                        | Aim of the Work                  | 3    |  |  |  |

|              | 1.3                        | Methodological Approach          | 4    |  |  |  |

|              | 1.4                        | Structure of the Work            | 5    |  |  |  |

| <b>2</b>     | Bac                        | kground                          | 7    |  |  |  |

|              | 2.1                        | C-ITS Standards and Security     | 7    |  |  |  |

|              | 2.2                        | Embedded Systems Security        | 8    |  |  |  |

|              | 2.3                        | Secure Hardware                  | 9    |  |  |  |

|              | 2.4                        | Boot Flow                        | 12   |  |  |  |

|              | 2.5                        | Threat Modeling for CPS          | 15   |  |  |  |

| 3            | Ana                        | lysis                            | 19   |  |  |  |

|              | 3.1                        | Frameworks                       | 19   |  |  |  |

|              | 3.2                        | Requirements Analysis            | 22   |  |  |  |

|              | 3.3                        | Threat and Risk Analysis         | 24   |  |  |  |

|              | 3.4                        | Market Survey                    | 29   |  |  |  |

|              | 3.5                        | Evaluation                       | 35   |  |  |  |

| <b>4</b>     | Concept and Implementation |                                  |      |  |  |  |

|              | 4.1                        | Concept Requirements             | 39   |  |  |  |

|              | 4.2                        | Key Management Approaches        | 40   |  |  |  |

|              | 4.3                        | Full System Concept              | 44   |  |  |  |

|              | 4.4                        | NXP iMX8 Boot & OP-TEE Setup     | 46   |  |  |  |

|              | 4.5                        | System Authentication by NXP     | 57   |  |  |  |

|              | 4.6                        | Key Management by TA             | 59   |  |  |  |

| <b>5</b>      | Evaluation |                            |    |  |  |  |

|---------------|------------|----------------------------|----|--|--|--|

|               | 5.1        | Security                   | 69 |  |  |  |

|               | 5.2        | Performance                | 75 |  |  |  |

|               | 5.3        | Services                   | 77 |  |  |  |

|               | 5.4        | Moving to Production       | 78 |  |  |  |

|               | 5.5        | Development Takeaways      | 79 |  |  |  |

| 6             | Sun        | nmary                      | 83 |  |  |  |

|               | 6.1        | Requirements and Analysis  | 83 |  |  |  |

|               | 6.2        | Concept and Implementation | 83 |  |  |  |

|               | 6.3        | Findings                   | 84 |  |  |  |

|               | 6.4        | Future Work                | 85 |  |  |  |

| $\mathbf{Li}$ | st of      | Figures                    | 87 |  |  |  |

| $\mathbf{Li}$ | st of      | Tables                     | 89 |  |  |  |

| $\mathbf{Li}$ | st of      | Listings                   | 91 |  |  |  |

| Acronyms      |            |                            |    |  |  |  |

| Bi            | bliog      | graphy                     | 97 |  |  |  |

## CHAPTER

## Introduction

#### 1.1 Motivation and Problem Statement

During recent years, the Internet of Things (IoT) emerged and internet-connected embedded systems are conquering the world in constantly rising numbers. Information sharing turned out to be an effective way to improve our increasingly dependent world. When it comes to transportation, passing messages from car to car or to their surroundings can highly improve safety, traffic flow and subsequently fuel efficiency, and provide improvements not only in current vehicles but also to support autonomous driving in the long run. To make this possible and support current cars with additional information, within the scope of Collaborative Intelligent Transport Systems (C-ITS) Vehicle-toeverything (V2X) communication is currently in the standardization process by established institutions, including the Institute of Electrical and Electronics Engineers (IEEE) and European Telecommunications Standards Institute (ETSI), in cooperation with international partners<sup>1</sup>. Devices compatible to the first standard publications are currently under heavy development throughout the transportation industry, and recently VW presented the first consumer product including this technology, their new Golf 8<sup>2</sup>.

Due to the basic communication structure, also the security requirements for the communication protocol are high and already standardized. The V2X communication structure is designed as a mesh-network, omitting a central point of authority. To keep it fast and simple, no sessions are used and information is directly broadcasted (and eventually received) by the various devices in near distance. This leads to the need of signing all messages sent to and verifying all messages received from participants, to provide message integrity. It can either be realized using WiFi (802.11p) or cellular (LTE-V2X,

<sup>&</sup>lt;sup>1</sup>https://www.etsi.org/technologies-clusters/technologies/automotiveintelligent-transport

<sup>&</sup>lt;sup>2</sup>https://www.forbes.com/sites/samabuelsamid/2019/10/28/volkswagen-includesnxp-v2x-communications-in-8th-gen-golf

in future 5G) networks. But there exist not only devices integrated in vehicles to provide information about their environment, the transportation infrastructure also needs to communicate with them. For this application, a dedicated type of C-ITS stations, so called Road Side Units (RSUs), are also currently under development. They are intended to be deployed at intersections and various other regions of interest, to communicate with the passing cars, informing them about their surroundings and supporting them with additional information, while being remotely administered and connected over the Internet<sup>3</sup>.

As they are basically embedded systems, designed as highly heterogeneous routing devices connected to the Internet, they have many different interfaces and run more or less typical IoT services. This requires a sophisticated and holistic security concept, as the effects of malicious manipulations can be catastrophic for traffic participants' safety, especially with the future goal of autonomous driving. The first generation of RSUs is currently used for development projects and the design for the second generation is on its way, planned to be used on a much bigger scale throughout Europe and the US.

The market of V2X devices is recently gaining attention and poses new requirements and services, while a lot of manufacturers are still struggling with securing their traditional IoT devices [1, 2]. The security problems in such devices are quite unique and promoted by resource constraints and cheap manufacturing cost targets. This often means barely or no updates at all. Additionally, these IoT devices are often operated out-of-sight and with potential physical access for attackers. This leads to unique threats targeted directly at the hardware level and therefore also demand countermeasures on hardware level, as software here is not enough any more. This work tries to build some knowledge about applied hardware-base security in this market by examining the following problems:

- What secure hardware suited for use within C-ITS stations is available and what functionality does it provide?

- Which typical C-ITS station services may gain security improvements by using such secure hardware and how can it be integrated into a system security concept?

A lot of research on security in embedded systems has been done recently. Cornerstones of a security concept are typically secure boot and storage [3]. To implement each of them, as also for other services, one needs some kind of secret keys or certificates. As these secrets now cannot be protected by a password supplied by a user, they have to be protected and managed in a different way without depending on external actions. Therefore, the hands-on part of this thesis will examine:

- What possibilities exist to securely do the key management in C-ITS stations using hardware support and what are their advantages and disadvantages?

- By using one of the possibilities of the last question, how well does the implementation and integration in a secure system work and where are the potential pitfalls?

<sup>&</sup>lt;sup>3</sup>https://new.siemens.com/global/en/products/mobility/road-solutions/ connected-mobility-solutions/sitraffic-vehicle2x.html

The last question also aims at building a solid understanding of the system and security concept, which shall later be used for further work in this area.

#### 1.2 Aim of the Work

The aim of this work is to enable and support security improvements by secure hardware in next-generation C-ITS stations. This is achieved by multiple steps.

#### 1.2.1 Market Survey

A market survey is conducted to build knowledge about available stand-alone and System on Chip (SoC) integrated secure hardware modules and to be able to examine their applicability in the upcoming next generation of C-ITS stations. It also aims at giving some guidance on potential security improvements and linking them to a usage in V2X communication specific services.

#### 1.2.2 PoC Implementation

In engineering, unknown problems tend to constantly arise during the design and implementation process of new devices. Therefore, one of the surveyed secure hardware modules is used to create a Proof of Concept (PoC), which shows how key management can be improved by using secure hardware (due to the limited scope, only one PoC was feasible). This fully aims at the applied security domain – to get an idea where the challenges are if one plans to integrate such devices in their products and at creating a well-documented basis for future integration and possible enhancements in other projects. The final evaluation shows us not only the security implications of the solution, but it also considers engineering metrics like portability, estimated implementation effort and software and documentation quality.

#### 1.2.3 Target Audience

The targeted audience is expected to have a broad knowledge on the computer science and information security domain, such as common terminology, cryptography, widespread threats and basic attacks. They should also have some background on hardware and its low-level software to be able to completely understand the topics in this work.

#### 1.3 Methodological Approach

The used methodology will be outlined in the following sections.

#### 1.3.1 Literature Review

As a solid base, a broad literature review is conducted. It builds some general knowledge about C-ITS devices and their security challenges, and shows us the state-of-the-art of embedded systems security in the domain of Cyber-Physical Systems (CPS) and the IoT. Threat modeling challenges for such devices and existing secure hardware are also addressed. On the basis of this review, the market survey is initiated.

#### 1.3.2 Market Survey

Existing stand-alone and SoC integrated secure hardware modules targeted more or less for automotive usage are gathered and examined for their provided features, interesting properties and special functionality to improve the security of C-ITS stations.

#### 1.3.3 System Analysis

To evaluate their potential impact on the system security, a requirement analysis and subsequently a Threat and Risk Analysis (TRA) are created for the examined system services. This is done in the context of a later integration in a system-wide standard currently developed and used for Industrial Automation Control Systems (IACS), the IEC 62443 [4], and picking an established and suitable TRA framework which can be used for embedded systems, namely Microsoft's STRIDE and DREAD. How they may be modified to fit the world of CPS is also briefly covered.

Knowing the requirements and TRA outcome, we now analyze the potential applicability to the system services and their potential security improvements. This shows, which threats can be addressed and to which extent they can be mitigated by the use of secure hardware to support further development decisions.

#### **1.3.4** PoC Implementation

To improve the security of the key management in C-ITS stations and assist a PoC implementation, various different concepts based on secure hardware of our preceding analysis are created. They get rated and one is picked for a hands-on PoC. The implementation is done using security best-practices and focusing on the applied security aspect, which is also considered in the final evaluation.

#### 1.4 Structure of the Work

This chapter outlines the motivation, formulates the existing problems to solve, and explains the used methodology. Some related work will be presented in the next chapter, chapter 2. It also includes an overview of common standards in the scope of this work and various general concepts, which will be used in the following chapters. The market survey is done in chapter 3, including a preceding explanation of the used framework for system analysis and the TRA. The evaluation of this analysis concludes this chapter. Based on this evaluation, different approaches to improve the system's key management are created in chapter 4 and a security concept is developed after rating and choosing one of them for a PoC implementation. Chapter 5 covers the evaluation of the concept in terms of security, performance and miscellaneous things worth noting. The last chapter of this work, chapter 6, summarizes the completed work and highlights open questions to be addressed in the future.

# CHAPTER 2

## Background

To create a solid basis of knowledge this thesis is built on, the following sections will list and explain related work and common concepts of C-ITS and embedded systems in the context of security. The focus will be on hardware concepts and features, as also modeling methods for threats.

#### 2.1 C-ITS Standards and Security

As this work exists in the context of C-ITS, some background on this topic is vital. Section 1.1 already introduced some high-level basics on V2X technology and C-ITS stations. On a lower level, in [5], Toetzl provides some basics for the used ETSI ITS-G5 standard, as also the used 802.11p WiFi layer described in ETSI ES 202 663 [6]. The communication is based on ad-hoc networks and does not support sessions for connections, therefore it needs to be embedded in a well-suited security concept. This results in the fact that every message has to be signed, requiring a sophisticated Public Key Infrastructure (PKI) as also described in [5]. Additional requirements on how the resulting keys and certificates have to be managed are specified by ETSI TS 102 940 [7], also including the C-ITS station communication security architecture and various defined security services on top of them. The Intelligent Transport Systems (ITS) station security management is also specified, as well as guidelines for establishing trust on such devices.

Various publications target the standards and their state of implementation [8, 9]. They give an overview over the standardization bodies involved and highlight, that due to the network structure, "in these environments, security is considered in design and implementation since compromised vulnerabilities in one vehicle can be propagated to other vehicles". However, there is always room for improvement. In [10], Gafencu et al. analyze special requirements for security (due to the very dynamic networks caused by moving nodes, the huge network scale, non-uniform distributed nodes and network

coverage) in ITS devices. Differences and similarities to the IoT are highlighted, and some measures for upcoming security improvements are proposed.

A recent development is also the aspired standardization of the European C-ITS market<sup>1</sup>, which was pushed forward by the European Union (EU) in 2019 by a delegated directive [11], that also covers additional security requirements in ANNEX 3. Although the directive was rejected by some of its member states<sup>2</sup>, the controversial topics did not include the specified security requirements. Therefore, we will likely see similar requirements in any future effort of standardizing the European market, although this will take additional time. In the meantime, a lot of big companies partnered up to adhere to many aspects of the rejected delegated directive due to the lack of other standards, as there exists a kind of consensus on the need of standards in this area.

#### 2.2 Embedded Systems Security

Given the fact that connected devices are constantly getting cheaper and are used for a growing number of applications, the topic of embedded systems security is gaining more and more momentum in recent years.

An overview of this is given by Papp et al. in [12]. They cover various threats and vulnerabilities of embedded systems, including their own attack taxonomy. According to that, the most successful approach by attackers is based on an internet-facing device, where either a vulnerable web application is running, the access control/authentication is weak or some other application with a basic programming error exists. Hardware is very rarely targeted, mostly it's applications or the firmware/Operating System (OS) itself. They want to support structural analysis and design of embedded systems, which is especially important as the physical protection of such devices is often hard to ensure and security highly affects their dependability and safety. In [13], Ravi et al. also examine general attack types and survey "tamper resistant designs", which shall help to prevent tampering with the device by either preventing, recovering or detecting attacks. This can be supported not only by software, but also by hardware. Another type of vulnerabilities which got a lot of attention lately is hardware-rooted. Mostly using Side-Channel Attacks (SCAs) to extract information from computer systems, these vulnerabilities hold whole new challenges for designing secure systems. In [14], Fournaris et al. are surveying potential microarchitectural attacks and outline some approaches to mitigate them. Except the original Rowhammer paper [15] they also mentioned, the Meltdown [16] and Spectre [17] vulnerabilities were gaining a lot of attention in 2018. Extending this research, the ZombieLoad [18] vulnerability was published in the following year, and also Rowhammer evolved to RAMBleed [19].

However, long before, the scientific community observed that the unique challenges of embedded systems security need a suitable design process, adapted models and new

<sup>&</sup>lt;sup>1</sup>https://ec.europa.eu/transport/themes/its/c-its\_en

<sup>&</sup>lt;sup>2</sup>https://agenceurope.eu/en/bulletin/article/12291/30

architectures. A lot of researchers were writing about design challenges in embedded systems and naming security a new dimension, that has already had to be considered throughout the whole development phase of embedded systems engineering [20, 21, 22]. However, years later, the state of security in embedded systems was still "a mess", as Viega et al. in [2] called it. They confirm the need of a different design approach from their data, but also acknowledge, that implementing security measures for new code is tough, for legacy code hard. They also mention, that due to the infrequent updates, these devices barely benefit from vulnerability management measures, what can be also seen in the survey of Pescatore et al. [1]. More about CPS design challenges was published aside a workshop of the Cyber Security Research Alliance (CSRA) [23]. The participants stress the role of security in such embedded systems, as the implications of failures may impair physical safety up to loss of life. They give recommendations on how to achieve this goal, even down to the supply chain.

When it comes to C-ITS and connected cars, as part of the IoT they face similar problems and challenges [24]. In [25], Roudier et al. bring the model-driven security approach to the automotive world, supported by a study during the E-safety Vehicle Intrusion Protected Applications (EVITA) project. And as cars get smarter and smarter, Markantonakis et al. in chapter 12 of [26] examine attackers and attack paths including threats, risks and privacy aspects of smart, embedded, automotive platforms. Soja in his white paper [27] outlines a different aspect – the application of standards to create good implementations. He argues, that due to the increasing connectivity, no safety without security exists any more, and therefore the industry must develop standards and design with the possibility of attacks in mind. As he lays the focus on the application, he outlines various security mechanisms, starting from secure flash programming, building a Chain of Trust (CoT) for secure boot and using dedicated cipher engines for external memory security. Other mechanisms, such as the importance of a good key management as well as general security best practices were examined by chapter 6 in [26]. Chapter 18 also highlights the advantages of well evaluated security implementations and methodology like Common Criteria (CC) to achieve that.

#### 2.3 Secure Hardware

Already before embedded systems conquered the world, security had been a problem which could not fully be solved by software. Over decades, the architecture of today's computers was extended and modified to fit new requirements, resulting in a sub-optimal design for security. Nowadays, hardware can provide an additional layer of security which software cannot, located even below the OS and providing tampering protection, defense against malicious software and side-channel mitigation. As Cheruvu et al. in [28] state, the important parts to achieve are the creation of a device identity, protected boot and protected storage. This can be achieved in various ways, leveraging special hardware as Trusted Platform Modules (TPMs) or a Trusted Execution Environment (TEE) supported by software. The following paragraphs will now make a short excursion to existing hardware security building blocks. Sanchez-Reillo et al. in [29] analyzed how to use "security hardware modules" to defeat upcoming security holes hardly addressable by software. Over the years, various hardware modules were established in the security domain, including TPMs, Mobile Trusted Modules (MTMs) and Hardware Security Modules (HSMs). Their basics are described in-depth in chapters 4 and 17 of [26]. TPMs, whose development and standardization is driven by the Trusted Computing Group (TCG), are used to provide cryptographic operations as also a Root of Trust (RoT) for storage, reporting and integrity measurement. In [30] also the Public Key Cryptography Standard #11 (PKCS#11) is mentioned, a industry standard API for cryptographic hardware. As requirements for mobile devices differ, MTMs take the place of a mobile version of TPM. HSMs take a similar role, they typically provide cryptographic functions and storage for cryptographic keys, including also tampering protection. In [31], Karter et al. evaluate various TPM security features and formulate key benefits, as there is the confidence in the platform, platform-bound data, owner privacy and control as also secure boot. Especially in the scope of embedded systems, Wolf et al. in [32] examine the usage of HSMs, as they argue that their hardware layer is particularly exposed to physical attacks where tamper-protected hardware helps to protect critical information. They also highlight, that hardware measures cannot help neither in case of software vulnerabilities nor in fundamentally flawed designs.

A survey on current crypto-processors and their applications was recently published by Sau et al. [33]. They give an overview of hardware related vulnerabilities and countermeasures and take a look at various TEE methods and multiple approaches for secure boot. They conclude that trusted boot, TEE and secured storage are the main features for reasonable system security. To generalize such approaches, Löhr et al. in [3] introduce security patterns for secure boot and secure storage, both important basic trusted computing concepts, aiming to enhance security by using a combination of trusted hard- and software components. Secure boot is the requirement for most system security solutions, whereas secure storage is vital for application-level security.

We have already heard about trusted computing and TEEs, which are used to support the design of complex and secure systems. A definition of a TEE is given by Sabt et al. in [34]. They describe it as an isolated and "tamper-resistant processing environment", in which applications can be securely executed. They take a look at the existing Advanced RISC Machine (ARM) TEE implementation, the ARM TrustZone<sup>3</sup>, and define some general TEE building blocks. Due to the huge distribution of ARM processors in the mobile world, the ARM TrustZone is the de-facto standard there. Its architectural design is described in [35]. Some early experiments using the TrustZone were documented by Winter et al. in [36]. Their focus lies at system-level development on inexpensive TrustZone-enabled hardware, also possible in class-room settings. The general design and implementation of embedded systems based on the TrustZone is examined by Yan-Ling et al. in [37] to eliminate security weaknesses and enhance safety practices. They propose a multi-policy access control mechanism with a secure reinforcement method, building on that their prototype achieves a rational combination of secure OS and trusted hardware. An

<sup>&</sup>lt;sup>3</sup>https://developer.arm.com/ip-products/security-ip/trustzone

overview of the architectural features and use cases is given by Ngabonziza et al. in [38]. They discuss details of different ARM architectures with TrustZone support, review their hardware and software implementation and conclude that they provide great flexibility, while avoiding the scenario of an all-mighty black box as a system controller. Quite recently, Pinto et al. also created a comprehensive survey on TrustZone [39]. Realizing that recent activities have significantly advanced its state, they conducted an in-depth study and analyzed the most relevant system weaknesses, aiming to help researchers and developers to familiarize with the concepts. Looking forward, they believe that the IoT has the potential to yield high-impact contributions and increases the awareness of TrustZone as a powerful security building block for embedded systems. As one of the new improvements, Zhao et al. in [40] propose a private user data protection mechanism based on identity authentication. Using this, it is possible for Trusted Applications (TAs) to perform identity authentication on normal world applications calling it, and therefore prevent potential user data leakage. Their results show that their solution can provide effective countermeasures.

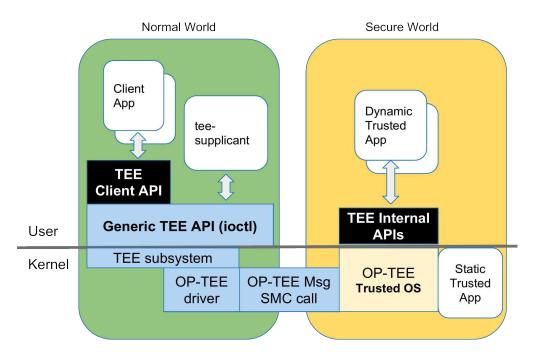

There exist numerous software implementations on top of the ARM TrustZone, created for different purposes. In an effort to make development of TAs for TEEs easier, the GlobalPlatform (GP) group created a standard for TEE core APIs [41]. Hence, the TAs can become independent of the underlying TEE implementation. Adhering to the GP standard, Open-TEE was created mostly as a research project and for development support [42]. It resembles a virtual, hardware-independent TEE implemented in software, which developers can use to develop and debug their TAs on. When the development finished, the source can easily be compiled for any other hardware TEE using the same standard. Such an other TEE implementation is the Open Platform Trusted Execution Environment (OP-TEE)<sup>4</sup>, supported by Linaro. It is open-source and has an extensive documentation online [43]. Therefore, it is gaining more and more attention now. Nehal et al. in [44] examined, how to secure IoT applications with OP-TEE. Due to its open-source character, they see OP-TEE as an important step to take security to every platform and as the future of securing IoT devices at hardware level. How to develop secure services for IoT devices with OP-TEE was also a topic of Göttel et al. in [45]. They implemented a key-value store and examined its performance and usability in contrast to the native secure storage implementation. Unsurprisingly, using secure storage goes hand in hand with a significant performance overhead.

In the C-ITS domain, the EVITA<sup>5</sup> project aims at "secure and trustworthy automotive on-board IT systems", as stated in their first publication [46]. Their approach of the security requirement analysis together with hard- and software design shall serve as a basis for future projects. One of their last publications [47] describes typical features of such systems and how secure keys should be handled in this context. They provide an analysis of their approach and also compare it to other cryptographic modules.

As security is not only about cryptography, there also exist other modules whose features

<sup>&</sup>lt;sup>4</sup>https://www.op-tee.org/

<sup>&</sup>lt;sup>5</sup>https://www.evita-project.org

can be leveraged to improve security. One of these are embedded Multi-Media Card (eMMC) modules, which can be more than a simple memory chip. They usually provide separate hardware partitions for boot and since its standard version 4.4 [48] also an Replay-Protected Memory Block (RPMB) partition. This can be leveraged against replay attacks, as Zilberstein et al. in [49] together with other eMMC features describe. It was also examined by Reddy et al. in [50], to protect secure data on mobile devices. Their proposed implementation guarantees secure storage against hacking attacks. Another quite interesting thing, though not ready for use yet, are Physically Unclonable Functions (PUFs). Also described in chapter 19 of [26], they can be used to uniquely identify and authenticate devices.

However, there is no hundred percent security, as also the recent publication of the TPM-FAIL attack by Moghimi et al. shows [51]. Hardware modules may introduce their own attack vectors and vulnerabilities. Some of the listed papers already include shortcomings of the examined modules and others focus solely on attacks, as Murdock et al. in [52] with the very recently discovered possibility of compromising Intel's TEE implementation via undervolting (named Plundervolt) or as Chen et al. in [53], where they describe a downgrade attack on the ARM TrustZone. They exploit reused verification keys and lacking rollback protection to achieve this. As some of these shortcomings are rooted in replay protection, RPMB may be leveraged to counter them. And not only technical shortcomings hinder the thriving of hardware security usage – as Batina et al. in [54] show on the example of TEEs, they still have unsolved technical issues on their own and licensing issues complicate their adoption. Keeping this in mind, however, as this section shows, we still have a lot of existing hardware security measures to improve the security state of embedded systems.

#### 2.4 Boot Flow

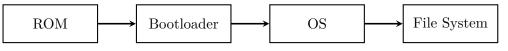

As we have seen in section 2.3, secure boot is considered a really important primitive of ensuring the security of computing devices. More on that in section 2.4.6, but first, here some background on the general boot process. An abstract schematics is given in figure 2.1, where one can see how a standard personal computer usually starts up to its using state.

Figure 2.1: Standard boot flow

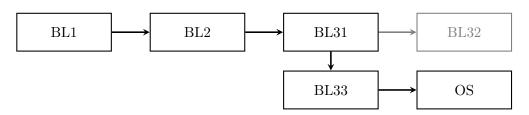

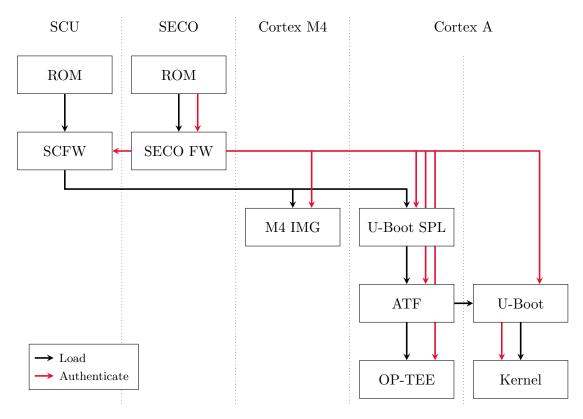

In embedded systems, this flow is highly dependent on the hardware platform used. However, the ARMv8 platform aims to define a standardized secure boot flow for all its processors, which system design is explained in the official documentation [55]. The ARMv8 AArch64 boot path can be seen in figure 2.2, its stages (or boot levels BL1,

Figure 2.2: ARMv8 AArch64 boot flow

| Non            | -trusted world | Trusted world  |       |  |

|----------------|----------------|----------------|-------|--|

| Level          | Software       | Software       | Level |  |

| EL0            | RA             | TA             | S-EL0 |  |

| $\mathrm{EL1}$ | ROS            | TOS            | S-EL1 |  |

| $\mathrm{EL2}$ | Hypervisor     | _              | _     |  |

| _              | _              | Secure monitor | EL3   |  |

Table 2.1: ARMv8 privilege execution levels (adapted from [56])

BL2, BL3-1, BL3-2 (optional) and BL3-3) are discussed in the following sections. The corresponding privilege levels used throughout the explanations are given in table 2.1.

#### 2.4.1 BL1: AP Trusted ROM

This denotes the usually fixed boot code in Read-Only Memory (ROM) and is typically supplied by the vendor of a SoC. It starts the boot path with the highest privilege level EL3 and performs various architectural and platform initialization tasks, such as initializing the CPU and its control registers, as also the console, watchdog, Memory Management Unit (MMU) and interconnect. It prepares the system state for loading the next stage, BL2.

#### 2.4.2 BL2: Trusted Boot Firmware

This denotes the so called Secondary Program Loader (SPL). It runs in S-EL1 and continues the architectural and platform initialization tasks. It also loads the subsequent images into Random-Access Memory (RAM) and hands over control to BL31.

#### 2.4.3 BL31: EL3 Runtime Software

This stage is solely executed in trusted SRAM on level EL3. A reference implementation according to the Trusted Board Boot Requirements [57] of ARM is available, the ARM Trusted Firmware (ATF). It performs mostly the same architectural initialization tasks as BL1 and allows to override any of the previous initializations done. Additionally, it continues the platform initialization and enables the power controller device. It

subsequently loads BL33, however, if a secure payload with corresponding Secure Payload Dispatcher (SPD) service is available, it also starts BL32.

#### 2.4.4 BL32: Secure-EL1 Payload (optional)

This stage is executed on level S-EL1 and often resembles a Trusted OS (TOS). It is implemented on top of a TEE, and continues to execute in parallel to the Rich OS (ROS) and its bootloader (see BL33 and subsequent stages). On ARM, it uses their TEE implementation named TrustZone, to run an isolated and secure OS with a small resource and code footprint which only loads signed TAs. An open-source implementation exists, called OP-TEE. More on that in section 4.4.6.

#### 2.4.5 BL33: Non-trusted Firmware

Executed on level EL1 or EL2, this stage resembles software which one may have in mind talking about traditional bootloaders. It finishes the system initialization and prepares everything for the start of the ROS, which will run in EL1. Most often, it also provides additional functionality for various support tasks. Again, an Open-Source implementation exists as U-Boot, which will be revisited in section 4.4.7. It is also described in chapter 9 of [58], where its concepts and setup to load an embedded Linux system are explained. This stage ends the standard boot process.

#### 2.4.6 Secure Boot

To get a secure or trusted boot process now, one has to leverage trusted computing, which uses hardware and software to provide security to the system. Patterns to use this for the boot process and subsequently also secure storage are presented by Löhr et al. in [3]. They label secure boot "the heart of most security solutions" and aim at presenting common patterns to enhance OS security. An example how this can be done using TPMs is also presented in chapter 6 of [30], and Kai et al. in [59] take this to embedded systems by using an MTM together with U-Boot and Linux. In [60], Khalid et al. write about the implementation of trusted boot for embedded system. As it is beneficial to integrate the whole functionality in one SoC, they use a Field-Programmable Gate Array (FPGA) to show the usefulness of their design against software attacks. However, they also state their solution does not help against physical attacks. A full review on different secure boot implementations flow of embedded applications was conducted by Rashmi et al. in [61].

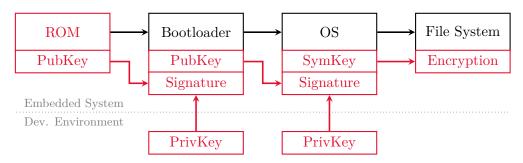

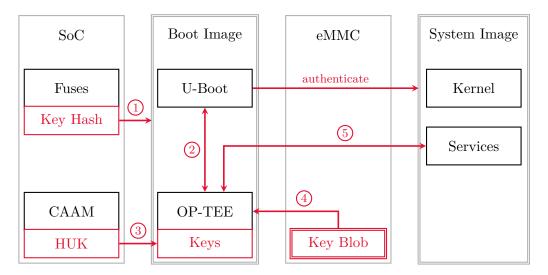

Establishing now a secure boot flow is all about building a CoT, starting with some RoT – typically, this is the initial bootloader code in the ROM of the SoC. To be able to authenticate code loaded later in time, a public key gets written to some write-once fuses. The ROM boot code uses this key to check the signature on the standard bootloader program. If the check fails, the ROM boot code rejects loading the bootloader. Otherwise, the bootloader itself checks the signature of the next software stage, the OS, extending the CoT. This way, it has to work for each step. The abstract schematics described

Figure 2.3: Chain of Trust example on generic secure boot flow

there can be seen in figure 2.3. Using this technique, also more boot flow stages can be used. However, including a file system poses a new challenge, as working with signatures typically does not work here. This will be outlined in the next section.

#### 2.4.7 CoT Extension

The state of a file system is constantly changing, as its purpose is persistent data storage. Therefore, the initial file system cannot just be signed and its signature checked while loading it to ensure its authentication. To achieve that, it needs to be encrypted. Different approaches exist in this area, it is possible to either encrypt the whole device below the file system layer (e.g. using  $cryptsetup^6$ ) or harness per-file file system level encryption (e.g.  $fscrypt^7$ ). One challenge they all have in common, though: On this kind of embedded systems we are talking about, there is no one to feed the encryption key (referred to as SymKey in figure 2.3) to the system. For security in personal computers, secure storage is widely aided by TPMs today. However, most of embedded systems do not provide the same modules and therefore have to use other techniques to securely store a file system master key and achieve secure storage. Storing a symmetric key in an (unencrypted) OS binary blob is inherently unsafe, therefore, another possibility has to be found for key management in such environments, satisfying various security and system requirements. This can be done, for example, by using trusted computing in file system development, as Jin et al. in [62] show. However, also if the master key is stored securely, one drawback remains: All the keys still remain in system memory while in operation. To further improve this, Yu et al. in [63] briefly outlined the idea of routing all file system encryption operations through an HSM. Although done in a server environment, this may turn out (partially) applicable for smaller systems.

#### 2.5 Threat Modeling for CPS

Nowadays, threat modeling is considered a standard tool in all development environments. As Adam Shostack put it in his famous book: "Threat modeling is the key to a focused

<sup>&</sup>lt;sup>6</sup>https://gitlab.com/cryptsetup/cryptsetup

<sup>&</sup>lt;sup>7</sup>https://www.kernel.org/doc/html/latest/filesystems/fscrypt.html

defense. Without threat modeling, you can never stop playing whack-a-mole."[64]. How to do it right is a different question, though. Starting with the increased publication of attack data over the Internet and through Computer Emergency Response Teams (CERTs), Moore et al. in [65] started with creating an approach of attack modeling. Aimed on security analysts and system designers, the patterns should help them to identify common attacks. However, threat modeling matured over the years, and today we got various different approaches as also a heterogeneous information system environment, each with their own recommendations.

Threat and risk modeling in vehicular systems was examined by Kadhirvelan et al. in [66]. Highlighting the connectedness of safety and security in vehicles, they analyze different methodologies and conclude, that all of these had to be modified to be applicable to standard vehicular systems. That shows, that choosing the right methods, adapted to the use case, is quite important. Another publication which shows this step-bystep for embedded systems in the automotive scope was provided by Hadding et al. [67]. To be able to compare the different existing methods, Shevchenko et al. recently summarized available modeling techniques, also mentioning CPS which may be vulnerable to nontraditional threats [68]. Overall, they reviewed 12 different threat modeling methods (which are not necessarily comprehensive) and do not recommend a special method, as this is a decision to take based on the needs of the project where it shall be used. Consecutively, in [69] they continue with an evaluation of the different methods for systems of CPS. The threat modeling method one chooses should fit one's system and target aspects, ranging from traditional to safety-related vulnerabilities and address kinetic, physical, cyber-physical, cyber-only, supply chain and insider threats. Finally, they recommend a combination of different methods including STRIDE.

The mnemonic of Spoofing, Tampering, Repudiation, Information Disclosure, Denial of Service, Elevation of Privilege (STRIDE) is mentioned in the bible of threat modeling by Adam Shostack, threat modeling: designing for security [64]. He covers the details of using STRIDE and all other things to watch out for while modeling threats in a system. The next book by Howard et al. is about its integration into the Microsoft Security Development Lifecycle (SDL) [70]. This is a 12-step process to ensure well-crafted security throughout the whole development process. For a further risk assessment, also a mnemonic of Damage, Reproducibility, Exploitability, Affected Users, Discoverability (DREAD) is covered here. STRIDE is often referred to as the most mature threat modeling method, therefore also a lot of work has already been done in this area. One is a descriptive study on STRIDE by Scandariato et al. in [71] to quantify its cost and effectiveness. Evaluating over three years, they found their results quite satisfying, although they admit an objective measurement is quite difficult. Also other methods were created on-top of STRIDE, as the hybrid threat modeling method by Mead et al. in [72]. coupling it with Security Cards and Persona non-Grata (PnG). For the domain of CPS, an approach was presented by Khan et al. in [73]. They propose a comprehensive five-step threat modeling framework built on STRIDE and Data-Flow Diagrams (DFDs) and finally state, that "STRIDE is a light-weight and effective threat modeling methodology

for CPS that simplifies the task for security analysts to identify vulnerabilities and plan appropriate component level security measures at the system design stage".

# CHAPTER 3

# Analysis

In the following sections, after explaining the used methodology, a generalized TRA will be conducted. This TRA will be used to examine, if and how available secure hardware targeted at V2X devices will be applicable to improve the security of C-ITS stations.

#### 3.1 Frameworks

Our methodology consists in applying existing and established frameworks, as also Soja et al. especially stated the need for standards in system design and development [27]. Some basics on them will be explained in this section, and we will add and define our adaptions here. The requirements are conducted accordingly to the IEC 62443, to make a later application to the full system possible. The TRA will use STRIDE and DREAD for CPS, loosely following the method in [73].

#### 3.1.1 System: IEC/ISA 62443

The standard IEC 62443, formerly known as ISA  $99^1$ , is a recently developed collection of standards (some parts are still under development, though), targeting IoT and CPS systems and claiming ISO 27001/27002 compatibility for easier integration in existing environments. It is targeting product suppliers, as well as system integrators and asset owners and deals with single components as also network systems.

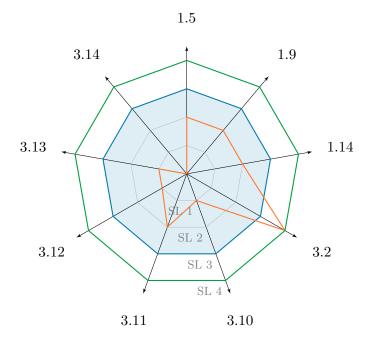

The basic concepts and terminology are explained in IEC 62443-1-1 [74]. It builds on defense-in-depth, "applying multiple countermeasures in a layered or stepwise manner", and also TRA recommendations including classes of threats. Taking a qualitative approach, general Security Levels (SLs) are recommended from 1 to 4. These levels are used to assess the targeted, achieved and capability SL.

<sup>&</sup>lt;sup>1</sup>https://www.isa.org/isa99/

| Level  | Intention | Resources | Skill | Motivation | Attacker Examples     |

|--------|-----------|-----------|-------|------------|-----------------------|

| SL $1$ | good      | 0         | 0     | 0          | Casual User           |

| SL $2$ | bad       | 0         | *     | 0          | Insider, Hacker       |

| SL $3$ | bad       | *         | •     | *          | Hacktivist, Terrorist |

| SL $4$ | bad       | •         | ٠     | •          | Nation States, APTs   |

• High, \* Medium,  $\circ$  Low

Table 3.1: IEC 62443 security levels

A summary of all SLs is given in table 3.1, they are defined as follows:

- SL 1: Prevent the unauthorized disclosure of information via eavesdropping or casual exposure.

- SL 2: Prevent the unauthorized disclosure of information to an entity actively searching for it using simple means with low resources, generic skills and low motivation.

- SL 3: Prevent the unauthorized disclosure of information to an entity actively searching for it using sophisticated means with moderate resources, IACS specific skills and moderate motivation.

- SL 4: Prevent the unauthorized disclosure of information to an entity actively searching for it using sophisticated means with extended resources, IACS specific skills and high motivation.

The core of the standard are the Foundational Requirements (FRs). These seven classes are subsequently used in the proceeding standards, such as IEC 62443-4-2 [75], defining "technical security requirements for IACS components". Meant for vendors of components for bigger systems, these seven FR groups containing multiple Component Requirements (CRs) including a baseline and Requirement Enhancements (REs) (to reach the targeted SL) are defined here. Specifically targeted on hardware are the following CRs:

- CR 1.5 Authenticator Management

- CR 1.9 Strength of public key-based authentication

- CR 1.14 Strength of symmetric key-based authentication

Also all of the six given Embedded Device Requirements (EDRs) apply here.

#### 3.1.2 Threat Analysis: STRIDE

A threat analysis typically starts with setting the scope and modeling the system, e.g. by its data flows. After this is done, the existing threats shall be found and categorized. STRIDE, already mentioned in section 2.5, is a mnemonic to assist in threat modeling.

The explanation of the single letters from [64] is:

- **Spoofing** is pretending to be something or someone you're not.

- **Tampering** is modifying something you're not supposed to modify. It can include packets on the wire (or wireless), bits on disk, or the bits in memory.

- **Repudiation** means claiming you didn't do something (regardless of whether you did or not).

- **Denial of Service** are attacks designed to prevent a system from providing service, including by crashing it, making it unusably slow, or filling all its storage.

- Information Disclosure is about exposing information to people who are not authorized to see it.

- Elevation of Privilege is when a program or user is technically able to do things that they're not supposed to do.

To find mitigation solutions afterwards, it is useful to assess the risk these threats pose to the system.

#### 3.1.3 Risk Analysis: DREAD

A risk assessment shall help with realizing the risk of different threats. However, one should keep in mind that, as hard as you may try, it "remains a statistical estimation that inherently includes uncertainties" [9]. DREAD, described in [76], is another mnemonic, helping you with estimating the risk. Its letters stand for:

- Damage Potential: How great is the damage if the vulnerability is exploited?

- **Reproducibility:** How easy is it to reproduce the attack?

- Exploitability: How easy is it to launch an attack?

- Affected Users: As a rough percentage, how many users are affected?

- Discoverability: How easy is it to find the vulnerability?

As also mentioned in a Microsoft blog  $\text{post}^2$ , DREAD got quite a bit of criticism. Therefore, we use a modified weighting approach here. First, our used rating includes four values from 0 (none) to 3 (high). Furthermore, as

$risk = damage \times probability$

we split DREAD into

damage =

$$\frac{1}{3}(Da + R + A)$$

probability

$$=\frac{1}{2}(E+Di)$$

which means, that both are now values from 0 to 3 and our overall risk contains values from 0 to 9. This may be interpreted as

•

$$0 \le v < 2$$

: low risk

- $2 \le v < 6$ : medium risk

- $6 \le v \le 9$ : high risk

<sup>&</sup>lt;sup>2</sup>https://blogs.msdn.microsoft.com/david\_leblanc/2007/08/14/dreadful/

# 3.2 Requirements Analysis

Although quite shallow, the rejected delegated directive [11] demands the use of a "secure hardware module" to protect secrets and enhance device security. The IEC 62443 standard is more specific here. Our targeted SL will be set to 3, covering most of the advanced attackers (see table 3.1). In the following, we give selected hardware-connected CRs and EDRs (and, if needed, their corresponding REs), which we will use as basic system requirements:

- CR 1.5 Authenticator Management RE (1) Hardware security for authenticators

- CR 1.9 Strength of public key-based authentication RE (1) Hardware security for public key-based authentication

- CR 1.14 Strength of symmetric key-based authentication RE (1) Hardware security for symmetric key-based authentication

- EDR 3.2 Protection from malicious code

- EDR 3.10 Support for updates RE (1) Update authenticity and integrity

- EDR 3.11 Physical tamper resistance and detection RE (1) Notification of a tampering attempt

- EDR 3.12 Provisioning product supplier roots of trust

- EDR 3.13 Provisioning asset owner roots of trust

- EDR 3.14 Integrity of the boot process RE (1) Authenticity of the boot process

The listed requirements above apply to the whole system, however, services running on the stations are another source of requirements, as they also often need confidentiality, integrity and availability. These will be covered in section 3.2.1.

Another requirement recently stressed by many is crypto agility. With a rapidly changing area of threats and the shadow of quantum computers (which will render today's asymmetric cryptography methods useless) above, building systems with hard-coded security features is not a good idea, and also projects in Europe have become aware of that. As Lonc et al. state, "they require capability to improve crypto-algorithms over time in C-ITS system which is a major issue in embedded systems due to constrained resources (i.e., Hardware Security Module, crypto-accelerators)" [8].

# 3.2.1 Services

In this section, typical C-ITS station services are gathered. A brief explanation is given, why and how they may profit from features provided by secure hardware.

#### Administration Front-End

Used mainly for convenient configuration and administrative purposes, a webserver is most often included in such devices. This means, it acts as a gate for users and should provide secure HTTP with Transport Layer Security (TLS) to provide confidentiality, integrity and privacy of the exchanged data. To provide TLS, the server possesses a root certificate (which is basically an accredited public key), signed by a certification authority, with which it now can prove its identity. The also included encryption is done by creating a symmetric session key with the help of the Diffie-Hellman (DH) key exchange. This now leads to a long-term certificate and short-term session keys which need protection.

#### Administration Back-End

Of course, administration is also often done through other channels. One thing they have in common is, that they are mainly also protected by adding a TLS layer, leading to the same protective needs as mentioned above. An example for this would be an API via the modern WebSocket protocol.

Another standard tool in administrating devices scattered over various locations are Virtual Private Networks (VPNs). As its name says, a VPN server creates a virtual network with all connected clients. To make the network "private" and ensure confidentiality and integrity, two main variants are common: Using Pre-Shared Keys (PSKs) or a PKI. The first variant denotes sharing a secret key which is used for authentication, the second variant works with certificates, which are created by the server. Each client gets one to prove their identity against the server, which checks if they are valid. Therefore, independent from the fact if the device takes the role of the server or the client, it either leaves us with a shared, secret key or a certificate for server/client authentication to protect.

#### Sensor Interfaces

Built for providing and routing data, the flexibility and extendability plays a big role for C-ITS stations. Therefore, they often provide interfaces to communicate with external sensors. However, as street- and intersection spaces can be huge, they may not be positioned directly at the station's position, so they typically use WiFi or Ethernet networks. Using best practice again, these are most likely also secured by adding a TLS layer, the protective needs of which we already covered.

#### V2X Communication

As mentioned in section 2.1, the secure part of V2X communication also relies on a PKI, although now with a different authority in contrast to TLS. Again, this means we have to protect a certificate used for signing outgoing messages.

#### Secure Storage

Secure storage is a service more integrated in the system and was also already mentioned in section 2.4.7. It is essential in ensuring the confidentiality and privacy of system and user data. As it cannot be integrated into the secure boot flow, it needs to get an extra (symmetric) key for its encryption. This key is ideally unique on a device basis and needs to be kept secret, therefore it is another asset to protect.

#### Key Management

As we see from the previous services, all to some extent demand a possibility to securely manage secret keys. This is also true for some system requirements of section 3.2, as the RoT of a secure boot implementation is just a private key which also needs integrity protection. Additionally, the same is true for confidential updates. Whereas updates can be authenticated by using a public key, the system has to be protected from altering it and confidential updates demand storing a symmetric key somewhere. This key also needs a good protection, as it may not be device unique. This would result in unique updates for every device, which is not feasible in practice.

Many applications providing one of the first three services (e.g. Nginx and OpenVPN) are compatible to OpenSSL and use it for their cryptographic operations, like en- and decrypting data, creating and verifying signatures and key exchange mechanisms like DH. OpenSSL already provides an API with the intention to make it easier to leverage secure hardware to extend the security of the performed operations. There also exist standardized cryptography interfaces like PKCS#11, which make it easier to find or create compatible software. These APIs may reduce the effort in making use of secure hardware for a lot of services, as they can further rely on their OpenSSL implementation, while OpenSSL relays all operations to a secure hardware module.

# 3.3 Threat and Risk Analysis

For the TRA, we will follow the steps below. They are recommended by [69] and slightly adapted:

- 1. Define technical scope

- 2. Decompose system and create model

- 3. Identify threats

- 4. Rate threats and calculate risk

- 5. Find mitigation

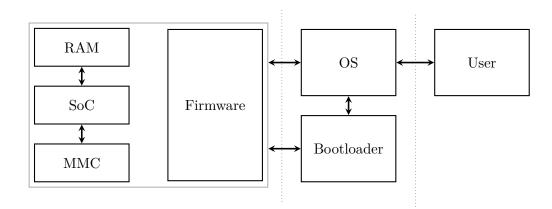

Figure 3.1: System model for TRA

#### 3.3.1 Scope

Our chosen scope is rather small, we will focus on threats which involve hardware or low-level software, as also the requirements in section 3.2 show. Therefore, we will not cover threats posed by application software or its implementation, as also specific threats of network devices. Additionally, we do not consider supply chain attacks and physical attacks on the SoC itself, as such kind of attacks require excellent skills, high effort and many resources and hence overshoot our required security level. Subsequently, we take a look at three different types of attackers: Attackers with physical access to the device, attackers with user access and – aligned with the defense in dept approach of IEC 62443 – attackers who already got root access on the system. Our modeled system is presented in the next section.

#### 3.3.2 System Model

"What are you building?" [64]

To start with modeling, you need to know your system at the right level of abstraction. Therefore, figure 3.1 shows the system model with its data-flow used in our subsequent TRA. The dotted lines depicture trust boundaries in between the modules. The mentioned attacker types strongly correspond to one or more components of the model. Components targeted by attackers with physical access are RAM and ROM, the component targeted by unprivileged attackers is the user space and the targets of privileged attackers are the OS and the bootloader.

# 3.3.3 Threat and Risk Modeling

"What can go wrong?" [64]

Using STRIDE and DREAD, the results of our TRA can be seen in table 3.2 and table 3.3. We can draw some interesting conclusions from that.

As high risk is defined as 6 and above, this includes:

- Threat 07: As the ROM is easier to exploit, similar threats (like 01 and 07) are more risky targeting the ROM. In general, the hardware components need some additional protection.

- Threats 12-19: Nearly all OS component threats combined with privileged attackers are extremely dangerous. A defense-in-depth approach can help us with that.

- Threats 22, 23 and 25: These threats show that securing updates is also very important, as they pose a great risk to the system.

Overall, the results definitely show a need for secret keys/certificate and update protection. Finally, as no threat is rated below risk 2, none of them can be considered low risk. Although the high effort for side-channel attacks lowers their risk, mitigation is strongly encouraged.

#### 3.3.4 Mitigation

"What should you do about those things that can go wrong?" [64]

After analyzing threats and their connected risk, hardware modules for threat mitigation are searched and examined. As we want to see which improvements hardware-based security features enable and which we can leverage, the next section will present some of them in a market survey.

26

| #  | Type | Comp. | Threat                                                 | Impact                               |

|----|------|-------|--------------------------------------------------------|--------------------------------------|

| 01 | Ι    | RAM   | read secret keys or<br>certificates offline            | control this and other devices       |

| 02 | D    | RAM   | destroy physically                                     | brick system                         |

| 03 | Т    | ROM   | modify FW/BL/OS offline                                | inject malware                       |

| 04 | Т    | ROM   | modify FW/BL/OS offline                                | reuse hardware                       |

| 05 | R    | ROM   | modify logs                                            | hide attack                          |

| 06 | Ι    | ROM   | modify FW/BL/OS offline                                | extract system information           |

| 07 | Ι    | ROM   | read secret keys or<br>certificates offline            | control this and other devices       |

| 08 | Ι    | ROM   | read FW/BL/OS offline                                  | explore potential<br>vulnerabilities |

| 09 | D    | ROM   | modify FW/BL/OS offline                                | brick system                         |

| 10 | D    | ROM   | destroy physically                                     | brick system                         |

| 11 | E    | ROM   | modify FW/BL/OS offline                                | control this device                  |

| 12 | S    | OS    | load own BL/OS                                         | control this device                  |

| 13 | Т    | OS    | modify FW/BL/OS                                        | inject malware                       |

| 14 | Т    | OS    | modify FW/BL/OS                                        | reuse hardware                       |

| 15 | R    | OS    | modify logs                                            | hide attack                          |

| 16 | Ι    | OS    | read secret keys or<br>certificates from ROM           | control this and other devices       |

| 17 | Ι    | OS    | read secret keys or<br>certificates from RAM           | control this and other devices       |

| 18 | Ι    | OS    | read FW/BL/OS                                          | explore potential<br>vulnerabilities |

| 19 | Ι    | OS    | modify FW/BL/OS                                        | extract system information           |

| 20 | D    | OS    | modify FW/BL/OS                                        | brick system                         |

| 21 | Т    | User  | modify RAM via SC                                      | control this device                  |

| 22 | Т    | User  | modify BL/OS update                                    | control this and other devices       |

| 23 | Т    | User  | use old BL/OS update                                   | restore vulnerable software          |

| 24 | Ι    | User  | read secret keys or<br>certificates from RAM via<br>SC | control this and other devices       |

| 25 | Ι    | User  | read BL/OS update                                      | explore potential<br>vulnerabilities |

Table 3.2: Threat Analysis

| #  | Da | R | Ε | Α | Di | Damage | Prob. | Risk |

|----|----|---|---|---|----|--------|-------|------|

| 01 | 3  | 3 | 2 | 3 | 1  | 3.0    | 1.5   | 4.5  |

| 02 | 1  | 3 | 3 | 1 | 3  | 1.7    | 3.0   | 5.0  |

| 03 | 3  | 3 | 2 | 2 | 2  | 2.7    | 2.0   | 5.3  |

| 04 | 3  | 3 | 2 | 2 | 2  | 2.7    | 2.0   | 5.3  |

| 05 | 1  | 3 | 2 | 2 | 2  | 2.0    | 2.0   | 4.0  |

| 06 | 3  | 3 | 2 | 2 | 2  | 2.7    | 2.0   | 5.3  |

| 07 | 3  | 3 | 2 | 3 | 2  | 3.0    | 2.0   | 6.0  |

| 08 | 1  | 3 | 2 | 2 | 2  | 2.0    | 2.0   | 4.0  |

| 09 | 1  | 3 | 2 | 1 | 2  | 1.7    | 2.0   | 3.3  |

| 10 | 1  | 3 | 3 | 1 | 3  | 1.7    | 3.0   | 5.0  |

| 11 | 3  | 3 | 2 | 2 | 2  | 2.7    | 2.0   | 5.3  |

| 12 | 3  | 3 | 3 | 2 | 3  | 2.7    | 3.0   | 8.0  |

| 13 | 3  | 3 | 3 | 2 | 3  | 2.7    | 3.0   | 8.0  |

| 14 | 3  | 3 | 3 | 2 | 3  | 2.7    | 3.0   | 8.0  |

| 15 | 1  | 3 | 3 | 2 | 3  | 2.0    | 3.0   | 6.0  |

| 16 | 3  | 3 | 3 | 3 | 3  | 3.0    | 3.0   | 9.0  |

| 17 | 3  | 3 | 3 | 3 | 3  | 3.0    | 3.0   | 9.0  |

| 18 | 1  | 3 | 3 | 2 | 3  | 2.0    | 3.0   | 6.0  |

| 19 | 3  | 3 | 3 | 2 | 3  | 2.7    | 3.0   | 8.0  |

| 20 | 1  | 3 | 3 | 1 | 3  | 1.7    | 3.0   | 5.0  |

| 21 | 3  | 2 | 1 | 2 | 1  | 2.3    | 1.0   | 2.3  |

| 22 | 3  | 3 | 2 | 3 | 3  | 3.0    | 2.5   | 7.5  |

| 23 | 2  | 3 | 3 | 2 | 3  | 2.3    | 3.0   | 7.0  |

| 24 | 3  | 2 | 1 | 3 | 1  | 2.7    | 1.0   | 2.7  |

| 25 | 1  | 3 | 3 | 2 | 3  | 2.0    | 3.0   | 6.0  |

Table 3.3: Risk Analysis

28

# 3.4 Market Survey

According to the requirement of using a "secure hardware module", the following pages will give an overview of several stand-alone and SoC-integrated modules.

# 3.4.1 Secure Hardware Modules

#### NXP SXF1800

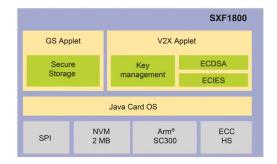

The SXF1800<sup>3</sup> is an HSM especially targeted at supporting standardized V2X communication as in IEEE 1609.6 and ETSI TS 103 097. Additionally, it provides long-term key storage for certificates and other data. Connected to the SoC via Serial Peripheral Interface (SPI), it provides 1MB of storage for user data. NXP claims crypto agility through secure firmware updates, supporting National Institute of Standards and Technology (NIST) and Brainpool Elliptic Curve Cryptography (ECC) curves. It is CC EAL5+ certified, compliant with the Car-to-Car (C2C) V2X HSM protection profile and the Federal Institute Processing Standards (FIPS) 140-2 level 3 requirements.

Figure 3.2: NXP SXF1800 HSM block diagram (www.nxp.com)

<sup>3</sup>https://www.nxp.com/products/wireless/dsrc-safety-modem/secure-elementic-for-v2x-communication:SXF1800

# Infineon Optiga TPM SLI 9670

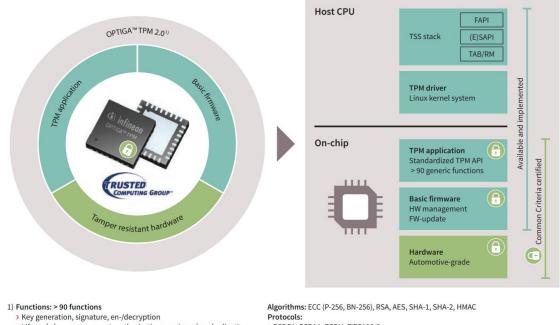

The Optiga TPM SLI 9670<sup>4</sup> is a TPM targeted on industrial and automotive applications and provides key store and management functionality. An overview is given in figure 3.3. The connection to the SoC is realized with SPI. Again, crypto agility through updateability is a topic here and the related Linux drivers are open-source. The currently supported cryptographic algorithms include HMAC, SHA1, SHA2, ECC (BN-256, P-256), AES and RSA [77]. The module conforms to the TCG standard TPM 2.0 and is certified according to CC EAL4+. Evaluation modules are available together with documentation on how to run these together with Linux on a Raspberry Pi 3 [78] and 4 [79].

> Life cycle key management, authorization, sessions, key duplication > Secure logging, secure time, secure boot, field-upgrade

> ECDSA, ECDAA, ECDH, FIPS186-3

> RSASSA\_PKCS1v1, RSASSA\_PSS, RSAEP, RSAES\_OAEP, RSAES\_PKCSV1

Figure 3.3: Infineon OPTIGA TPM software and features [80]

<sup>4</sup>https://www.infineon.com/cms/de/product/security-smart-card-solutions/ optiga-embedded-security-solutions/optiga-tpm/sli-9670/

30

# 3.4.2 SoCs

# Autotalks Craton 2

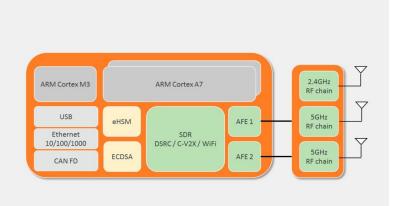

The Craton 2 platform<sup>5</sup> was specifically designed for connected vehicles. Created by the Israeli company Autotalks, this resembles a product not built from one of the two big manufacturers in this market and marketed as a cost-optimized solution. It combines a 32-bit dual-core ARM Cortex A7 with a WiFi modem supporting 802.11p, a Cellular V2X (C-V2X) modem and a specialized V2X HSM. This HSM supports ECDSA and various hardware accelerators. They claim to be the first and only company supporting both competing V2X technologies in a single SoC. Pre-integrated software is available. An evaluation kit is ready to purchase, however, overall not a lot of information could be found on the SoC.

Figure 3.4: Autotalks Craton 2 block diagram (www.elektronikpraxis.vogel.de)

<sup>5</sup>https://www.auto-talks.com/product/craton2/

# Infineon AURIX TriCore TC3xx

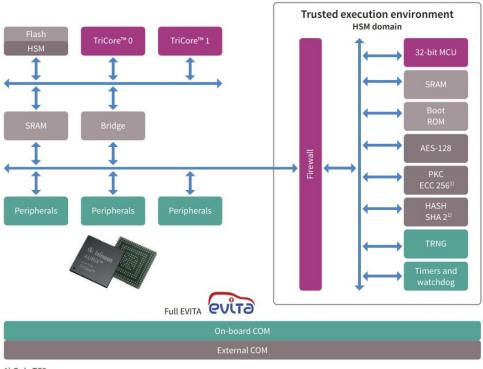

The AURIX TriCore TC3xx<sup>6</sup> SoC family is the most recent and powerful microcontroller product line of Infineon. Consisting of numerous different types containing up to 6 cores, their "TriCores" are 32-bit RISC cores running at about 300MHz. The documentation [81] includes an explanation of their security features and a lot more information. On the hardware side, an HSM is embedded, which can be used for storing cryptographic keys and also includes dedicated hardware accelerators (supporting AES128, ECC256 and SHA2). They also claim crypto agility for their HSM implementation, as it is programmable via software. Due to the flexibility of their HSM, trusted customized vendor apps are possible, which are executed in a TEE on the HSM. Additionally, a partly open-source software stack including a complete toolchain is provided by them. The embedded HSM fulfills the full EVITA standard. Various "Triboards", their evaluation kits, are available to support the development.

1) Only TC3xx

Figure 3.5: Infineon Auric TriCore security diagram (www.infineon.com)

<sup>&</sup>lt;sup>6</sup>https://www.infineon.com/cms/de/product/microcontroller/32-bit-tricoremicrocontroller/

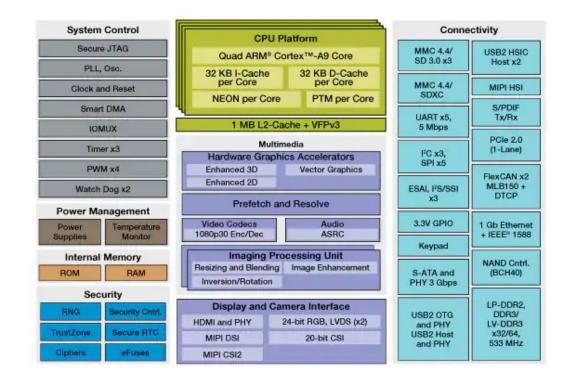

# NXP i.MX6

The i.MX6<sup>7</sup> SoC family is well-established and widely used in industry and automotive products. It consists of 9 different variants, built around up to four 32-bit ARM Cortex A7 or A9 cores, running at a speed of about 1GHz. An NXP implementation for secure boot is available, called High Assurance Boot (HAB)v4, as also a cryptographic cipher engine module called Cryptographic Assertion and Assurance Module (CAAM). A lot more information can be found in its reference manual [82]. The current software stack is extensive and mainly open-source [83]. It includes U-Boot, OP-TEE and Linux Kernel version 4.14. Various evaluation kits are available for testing.

Figure 3.6: NXP i.MX8 SoC features (www.nxp.com)

<sup>7</sup>https://www.nxp.com/products/processors-and-microcontrollers/armprocessors/i.mx-applications-processors/i.mx-6-processors:IMX6X\_SERIES

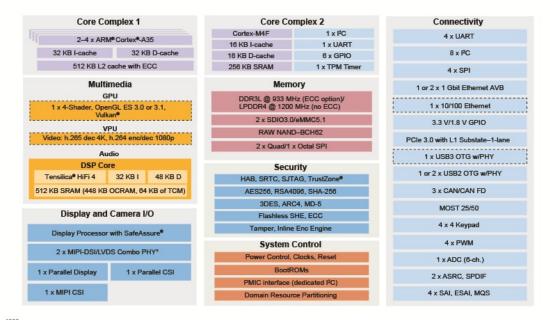

#### NXP i.MX8